2. SMBus features

2.1. SMBus standard

The interface is compliant with the SMBus version 2.0 standard. However not all features of this standard are supported. For more information on the SMBus 2.0 standard, please refer to the SMBus specification.

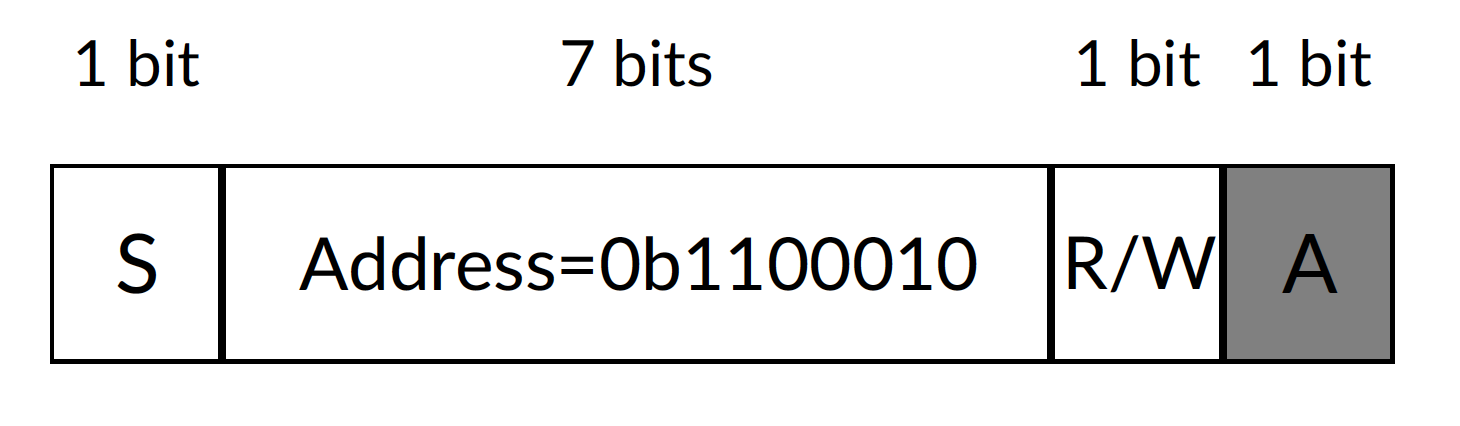

2.2. Device address

The 7-bit device address is 0x62. It is defined as a fixed slave address by the SMBus standard.

This address has been verified to not overlap with any reserved address specified in the SMBus 2.0 standard. It appears on the I2C bus as:

2.3. Device type

The device is an SMBus slave, in other words it receives commands and responds to them.

The device can be categorized as Non-ARP-capable according to the SMBus 2.0 standard.

2.4. Interface speed

The interface speed is limited to 100 kHz in accordance with the SMBus 2.0 standard.

2.5. Interface topology

Each PCIe card should be connected to the chassis on a dedicated SMBus interface. In other words, multiple SMBus slaves with this address should not be wired onto the same bus to prevent address conflicts.

2.6. Supported features

The following SMBus 2.0 bus protocols are supported. More details can be found in the SMBus 2.0 specification, including transaction diagrams to describe each of the protocols.

Write Word

Read Word

Block Write

Block Read

Block Process Call

Some commands support both Block Read and Block Write to the same command. See the command descriptions for more details.

As outlined in the specification, a Block Read or Block Write is allowed to transfer a maximum of 32 data bytes, while for a Block Process Call the combined data payload must not exceed 32 bytes.

Also note that the data returned by a Block Read (or the read portion of a Block Process Call) is preceeded by a byte count byte, meaning that the number of bytes to be read will be the payload length (as defined by the command descriptions) + 1.

The device supports Packet Error Checking (PEC) as defined in section 5.4 of the SMBus 2.0 specification.

2.7. Unsupported features

The following are notable SMBus 2.0 features that are not supported, among others.

Since Address Resolution Protocol (ARP) is not supported, the PCIe card should be the only SMBus slave on the bus with this address.

Since Host Notify Protocol (HNP) is not supported, the PCIe card cannot alert the chassis. It is the responsibility of the chassis to poll the PCIe card.

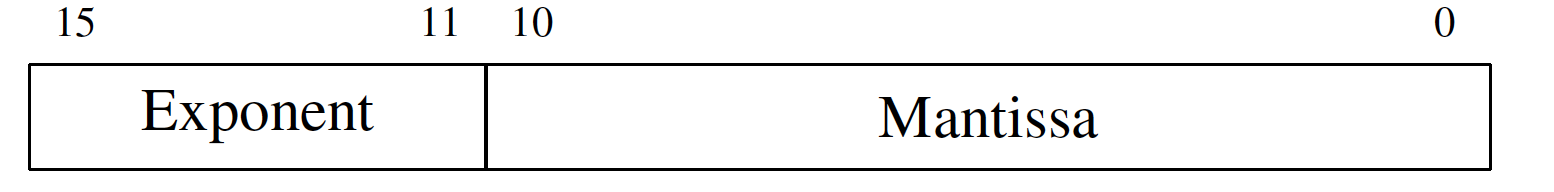

2.8. Linear11 format

Some readings, for example voltages, currents and temperatures, are sent in Linear11 data format.

The linear data format is a two byte value structured as follows:

It can be converted back to a decimal value with the following equation:

2.9. Command layout

The commands are grouped together into subsections. New commands will either be appended to existing subsections if appropriate, or added to a new subsection.

New SMBus commands will take a unique register value (from 0x00-0xFF) in order to preserve compatibility with previous versions.

The command set is linked to the API version. When adding commands, the API version will be incremented and listed along with the ICU version it was introduced in.

A single command may return multiple values to reduce host read cycles (for example values from temperature sensors). If new values are added to a block read, they will be appended to the end of an existing block, or added to a new block. Values that are no longer relevant will remain, but will return a dummy value. The API version allows the host to determine the relevant returned data.